6000 Teutonia Avenue, Milwaukee, WI 53209 USA Tel: (800) 231-8327 (414) 438-3850 Fax: (414) 438-4234 email: techservice@sial.com\_sigma-aldrich.com

# **Product Information**

## Poly[bis(4-phenyl)(2,4,6-trimethylphenyl)amine]

Catalog Number **702471**Store at Room Temperature

Technical Bulletin AL-254

## **TECHNICAL BULLETIN**

Synonyms: Poly(triaryl amine), PTAA

### **Product Description**

$[C_6H_4N(C_6H_2(CH_3)_3)C_6H_4]_n$

Poly[bis(4-phenyl)(2,4,6-trimethylphenyl)amine] is an amorphous p-type polymer semiconductor. 1.2 It may be used to fabricate field-effect transistors (FETs).

PTAA is also useful as a hole transport material in organic light emitting diodes (OLEDs).

#### **Precautions and Disclaimer**

This product is for R&D use only, not for drug, household, or other uses. Please consult the Material Safety Data Sheet for information regarding hazards and safe handling practices.

## Storage/Stability

Store the product at room temperature.

#### **Procedure**

Fabrication of PTAA field-effect transistors (FETs) Bottom-gate bottom-contact FETs were fabricated in a nitrogen atmosphere on highly doped Si-wafers with a thermally grown 250 nm SiO<sub>2</sub> layer. The two layers served as the gate electrode and gate insulator. Au source and drain electrodes (30 nm thick) were defined by standard photolithography:

channel length (L) = 10  $\mu$ m channel width (W) = 10 mm

Prior to deposition of the PTAA polymer layer, the Si-wafers were treated with octyltrichlorosilane (OTS-18, Catalog Number 104817) by immersing them in 10 mM solutions in toluene for 15 minutes at 60 °C.

A homogeneous solution of PTAA was prepared in toluene at room temperature containing 1.0 wt% of the polymer. This solution was deposited via spin-coating at 500 rpm for 30 seconds followed by 2,000 rpm for 50 seconds.

#### Results

Electrical characterization of the PTAA FETs was conducted in a nitrogen atmosphere with a HP4155B semiconductor parameter analyzer. Field-effect mobilities were calculated from transfer characteristics (saturation regime) employing the relation:<sup>3</sup>

$$\frac{\delta I_{sd}(V_g)}{dV_g} = \frac{C_i \cdot W}{L} \mu_{FET}(V_g, V_{sd}) \cdot (V_g - V_0)$$

$I_{\rm sd}$  is the source-drain current (saturation regime)  $V_{\rm g}$  and  $V_{\rm sd}$  gate and source-drain voltage, respectively  $C_{\rm i}$  the insulator capacitance W and L the channel width and length  $V_{\rm 0}$  the turn-on voltage

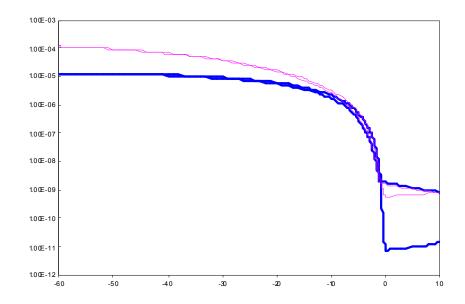

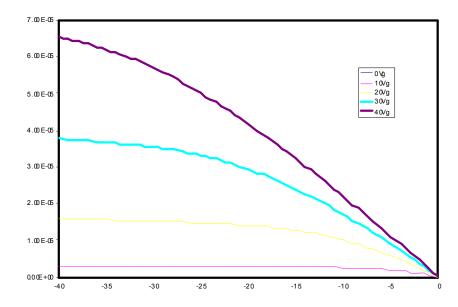

Transfer and output curves for PTAA transistors are shown in Figures 1 and 2.

Figure 1. Transfer output curves for PTAA transistors corresponding to field effect mobility of  $4 \times 10^{-3}$  cm<sup>2</sup>/Vs.

**Figure 2.** Output curves for PTAA transistors corresponding to field effect mobility of  $4 \times 10^{-3}$  cm<sup>2</sup>/Vs.

#### References

- 1. Chabinyc, M.L. et al., MRS Bull., 7th ed., **33**, 683, (2008)

- 2. Veres, J. et al., Adv. Funct. Mater., 13, 199, (2003).

- 3. Brown, A.R. et al., Synth. Met., 88, 37 (1997).

Data courtesy of Dr. Iain McCulloch, Imperial College London and Flexink, Inc.

BF,IK,MAM 02/09-1